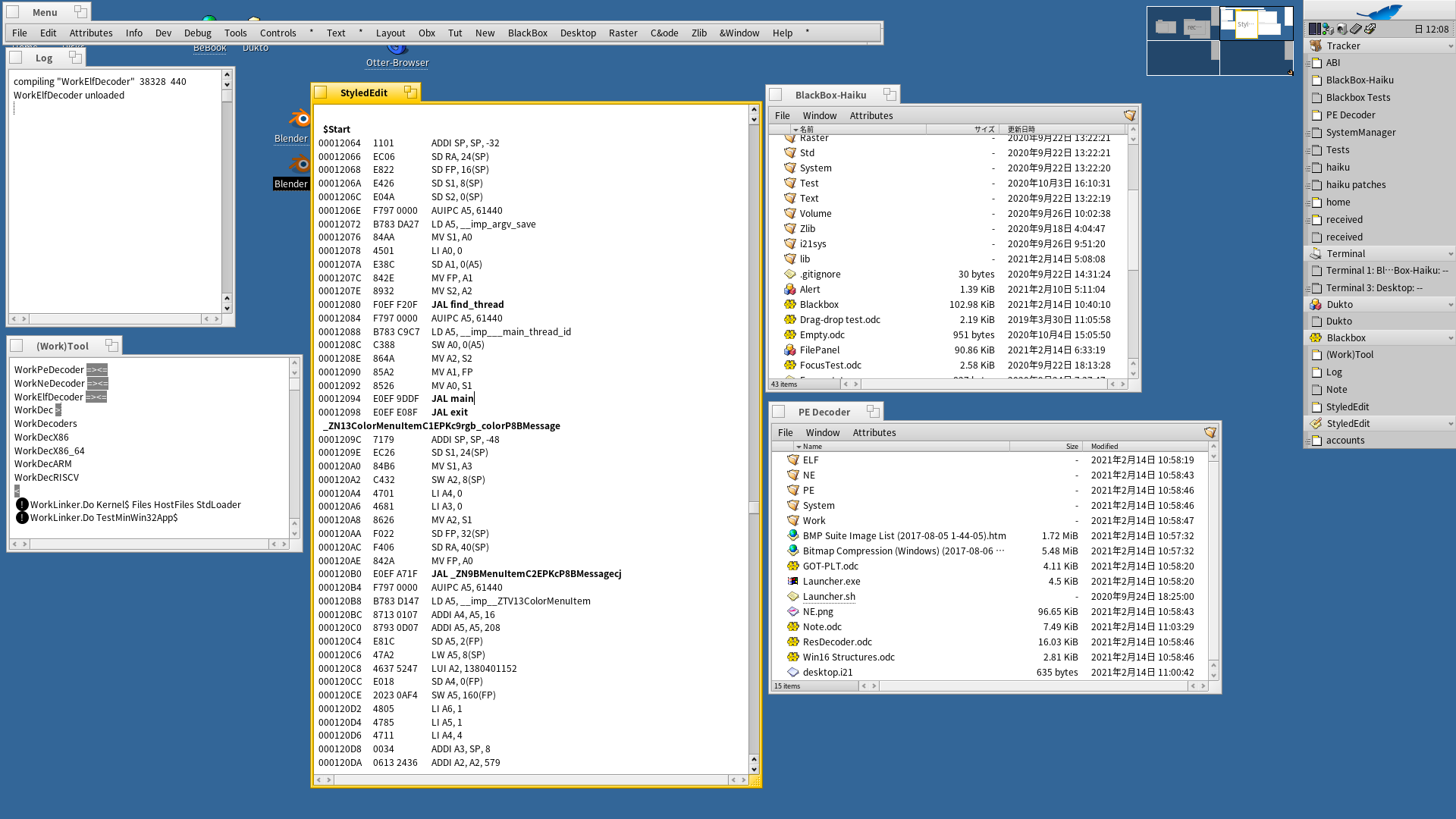

I recently wrote RISC-V disassembler in Oberon from scratch in 2 days. Source code is here. BlackBox on Haiku is needed to run. It seems to be complete but it can be inaccurate (especially FPU, llvm-objdump that I used as reference can’t decode FPU instructions). It can resolve symbol references and PIC stubs.

RISC-V use bit mixing a lot and I don’t know why. For example single continuous block is mixed into 8 (!) parts for short JAL instruction:

001 imm[11|4|9:8|10|6|7|3:1|5] 01 C.JAL (RV32)

imm := SignExtend(

op[0] DIV ASH(1, 2) MOD ASH(1, 1)*ASH(1, 5) +

op[0] DIV ASH(1, 3) MOD ASH(1, 3)*ASH(1, 1) +

op[0] DIV ASH(1, 6) MOD ASH(1, 1)*ASH(1, 7) +

op[0] DIV ASH(1, 7) MOD ASH(1, 1)*ASH(1, 6) +

op[0] DIV ASH(1, 8) MOD ASH(1, 1)*ASH(1, 10) +

op[0] DIV ASH(1, 9) MOD ASH(1, 2)*ASH(1, 8) +

op[0] DIV ASH(1, 11) MOD ASH(1, 1)*ASH(1, 4) +

op[0] DIV ASH(1, 12) MOD ASH(1, 1)*ASH(1, 11)

, 12);