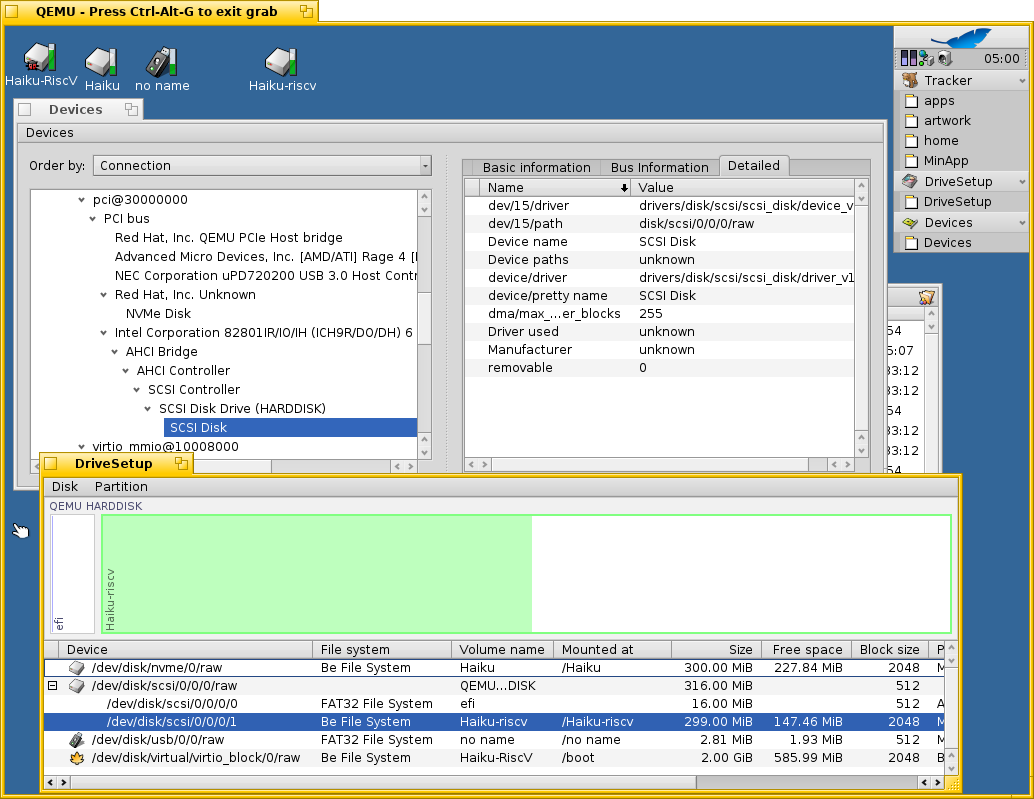

AHCI (SATA disks) are working. The problem was here in “packed” struct attribute that cause per-byte access to MMIO registers instead of 32 bit access.

Also PCI register allocator was improved to support proper alignment (register addresses should be aligned with reported register size). Some hardcoding was removed.

PCI bus related kernel serial output:

pci_controller_init()

reg[0]: (0x30000000, 0x10000000)

interrupt-map:

bus: 0, dev: 0, fn: 0, childIrq: 1, parentIrq: (3, 32)

bus: 0, dev: 0, fn: 0, childIrq: 2, parentIrq: (3, 33)

bus: 0, dev: 0, fn: 0, childIrq: 3, parentIrq: (3, 34)

bus: 0, dev: 0, fn: 0, childIrq: 4, parentIrq: (3, 35)

bus: 0, dev: 1, fn: 0, childIrq: 1, parentIrq: (3, 33)

bus: 0, dev: 1, fn: 0, childIrq: 2, parentIrq: (3, 34)

bus: 0, dev: 1, fn: 0, childIrq: 3, parentIrq: (3, 35)

bus: 0, dev: 1, fn: 0, childIrq: 4, parentIrq: (3, 32)

bus: 0, dev: 2, fn: 0, childIrq: 1, parentIrq: (3, 34)

bus: 0, dev: 2, fn: 0, childIrq: 2, parentIrq: (3, 35)

bus: 0, dev: 2, fn: 0, childIrq: 3, parentIrq: (3, 32)

bus: 0, dev: 2, fn: 0, childIrq: 4, parentIrq: (3, 33)

bus: 0, dev: 3, fn: 0, childIrq: 1, parentIrq: (3, 35)

bus: 0, dev: 3, fn: 0, childIrq: 2, parentIrq: (3, 32)

bus: 0, dev: 3, fn: 0, childIrq: 3, parentIrq: (3, 33)

bus: 0, dev: 3, fn: 0, childIrq: 4, parentIrq: (3, 34)

ranges:

IOPORT (0x01000000): child: 00000000, parent: 03000000, len: 10000

MMIO32 (0x02000000): child: 40010000, parent: 40010000, len: 3f000000

MMIO64 (0x03000000): child: 400000000, parent: 400000000, len: 400000000

AllocRegs()

AllocRegsForDevice(bus: 0, device: 0, function: 0)

bar[0]: MMIO32, adr: 0x0, size: 0x0

bar[1]: MMIO32, adr: 0x0, size: 0x0

bar[2]: MMIO32, adr: 0x0, size: 0x0

bar[3]: MMIO32, adr: 0x0, size: 0x0

bar[4]: MMIO32, adr: 0x0, size: 0x0

bar[5]: MMIO32, adr: 0x0, size: 0x0

rom_bar: adr: 0x0, size: 0x0

intLine: 32

intPin: -

AllocRegsForDevice(bus: 0, device: 1, function: 0)

bar[0]: MMIO32, adr: 0x0, size: 0x1000000 -> 0x41000000

bar[1]: IOPORT, adr: 0x0, size: 0x100 -> 0x100

bar[2]: MMIO32, adr: 0x0, size: 0x4000 -> 0x42000000

bar[3]: MMIO32, adr: 0x0, size: 0x0

bar[4]: MMIO32, adr: 0x0, size: 0x0

bar[5]: MMIO32, adr: 0x0, size: 0x0

rom_bar: adr: 0x0, size: 0x10000 -> 0x42010000

intLine: 33

intPin: INTA#

AllocRegsForDevice(bus: 0, device: 2, function: 0)

bar[0]: MMIO64, adr: 0x0, size: 0x4000 -> 0x400000000

bar[2]: MMIO32, adr: 0x0, size: 0x0

bar[3]: MMIO32, adr: 0x0, size: 0x0

bar[4]: MMIO32, adr: 0x0, size: 0x0

bar[5]: MMIO32, adr: 0x0, size: 0x0

rom_bar: adr: 0x0, size: 0x0

intLine: 34

intPin: INTA#

AllocRegsForDevice(bus: 0, device: 3, function: 0)

bar[0]: MMIO64, adr: 0x0, size: 0x4000 -> 0x400004000

bar[2]: MMIO32, adr: 0x0, size: 0x0

bar[3]: MMIO32, adr: 0x0, size: 0x0

bar[4]: MMIO32, adr: 0x0, size: 0x0

bar[5]: MMIO32, adr: 0x0, size: 0x0

rom_bar: adr: 0x0, size: 0x0

intLine: 35

intPin: INTA#

AllocRegsForDevice(bus: 0, device: 4, function: 0)

bar[0]: MMIO32, adr: 0x0, size: 0x0

bar[1]: MMIO32, adr: 0x0, size: 0x0

bar[2]: MMIO32, adr: 0x0, size: 0x0

bar[3]: MMIO32, adr: 0x0, size: 0x0

bar[4]: IOPORT, adr: 0x0, size: 0x20 -> 0x200

bar[5]: MMIO32, adr: 0x0, size: 0x1000 -> 0x42020000

rom_bar: adr: 0x0, size: 0x0

intLine: 32

intPin: INTA#

PCI: [dom 0, bus 0] bus 0, device 0, function 0: vendor 1b36, device 0008, revision 00

PCI: class_base 06, class_function 00, class_api 00

PCI: line_size 00, latency 00, header_type 00, BIST 00

PCI: ROM base host 00000000, pci 00000000, size 00000000

PCI: cardbus_CIS 00000000, subsystem_id 1100, subsystem_vendor_id 1af4

PCI: interrupt_line 20, interrupt_pin 00, min_grant 00, max_latency 00

PCI: base reg 0: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 1: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 2: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 3: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 4: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 5: host 00000000, pci 00000000, size 00000000, flags 00

PCI: Capabilities: (not supported)

PCI: [dom 0, bus 0] bus 0, device 1, function 0: vendor 1002, device 5046, revision 00

PCI: class_base 03, class_function 00, class_api 00

PCI: line_size 00, latency 00, header_type 00, BIST 00

PCI: ROM base host 42010000, pci 42010000, size 00010000

PCI: cardbus_CIS 00000000, subsystem_id 1100, subsystem_vendor_id 1af4

PCI: interrupt_line 21, interrupt_pin 01, min_grant 00, max_latency 00

PCI: base reg 0: host 41000000, pci 41000000, size 01000000, flags 08

PCI: base reg 1: host 00000100, pci 00000100, size 00000100, flags 01

PCI: base reg 2: host 42000000, pci 42000000, size 00004000, flags 00

PCI: base reg 3: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 4: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 5: host 00000000, pci 00000000, size 00000000, flags 00

PCI: Capabilities: (not supported)

PCI: [dom 0, bus 0] bus 0, device 2, function 0: vendor 1033, device 0194, revision 03

PCI: class_base 0c, class_function 03, class_api 30

PCI: line_size 00, latency 00, header_type 00, BIST 00

PCI: ROM base host 00000000, pci 00000000, size 00000000

PCI: cardbus_CIS 00000000, subsystem_id 1100, subsystem_vendor_id 1af4

PCI: interrupt_line 22, interrupt_pin 01, min_grant 00, max_latency 00

PCI: base reg 0: host 00000000, pci 00000000, size 00004000, flags 04

PCI: base reg 1: host 00000004, pci 00000004, size 00000000, flags 00

PCI: base reg 2: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 3: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 4: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 5: host 00000000, pci 00000000, size 00000000, flags 00

PCI: Capabilities: MSI-X, PCIe, MSI

PCI: Extended capabilities: (empty list)

PCI: [dom 0, bus 0] bus 0, device 3, function 0: vendor 1b36, device 0010, revision 02

PCI: class_base 01, class_function 08, class_api 02

PCI: line_size 00, latency 00, header_type 00, BIST 00

PCI: ROM base host 00000000, pci 00000000, size 00000000

PCI: cardbus_CIS 00000000, subsystem_id 1100, subsystem_vendor_id 1af4

PCI: interrupt_line 23, interrupt_pin 01, min_grant 00, max_latency 00

PCI: base reg 0: host 00004000, pci 00004000, size 00004000, flags 04

PCI: base reg 1: host 00000004, pci 00000004, size 00000000, flags 00

PCI: base reg 2: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 3: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 4: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 5: host 00000000, pci 00000000, size 00000000, flags 00

PCI: Capabilities: MSI-X, PCIe

PCI: Extended capabilities: (empty list)

PCI: [dom 0, bus 0] bus 0, device 4, function 0: vendor 8086, device 2922, revision 02

PCI: class_base 01, class_function 06, class_api 01

PCI: line_size 00, latency 00, header_type 00, BIST 00

PCI: ROM base host 00000000, pci 00000000, size 00000000

PCI: cardbus_CIS 00000000, subsystem_id 1100, subsystem_vendor_id 1af4

PCI: interrupt_line 20, interrupt_pin 01, min_grant 00, max_latency 00

PCI: base reg 0: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 1: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 2: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 3: host 00000000, pci 00000000, size 00000000, flags 00

PCI: base reg 4: host 00000200, pci 00000200, size 00000020, flags 01

PCI: base reg 5: host 42020000, pci 42020000, size 00001000, flags 00

PCI: Capabilities: MSI, SATA