Hello

As I mentioned I am finding myself with an MMU preconfigured in EL2. That has been useful to understand the MMU itself and how it is being configured. Out of that and digging some ARMv8 documentation:

[...]

phys: 0xfbd26000-0xfcf30000, virt: 0xfbd26000-0xfcf30000, size = 0x120a000, type: LoaderData (0x2), attr: 0x8

phys: 0xfcf30000-0xfcf31000, virt: 0xfcf30000-0xfcf31000, size = 0x1000, type: ReservedMemoryType (0x0), attr: 0x8

phys: 0xfcf31000-0xfcfc0000, virt: 0xfcf31000-0xfcfc0000, size = 0x8f000, type: LoaderData (0x2), attr: 0x8

phys: 0xfcfc0000-0xfcfd0000, virt: 0xfcfc0000-0xfcfd0000, size = 0x10000, type: RuntimeServicesCode (0x5), attr: 0x8000000000000008

phys: 0xfcfd0000-0xfe800000, virt: 0xfcfd0000-0xfe800000, size = 0x1830000, type: LoaderData (0x2), attr: 0x8

phys: 0xfe800000-0x100000000, virt: 0xfe800000-0x100000000, size = 0x1800000, type: BootServicesData (0x4), attr: 0x8

phys: 0x880000000-0x8e0000000, virt: 0x880000000-0x8e0000000, size = 0x60000000, type: BootServicesData (0x4), attr: 0x8

Efi loader symbols offset: 0xfbcc0000:

Current Exception Level EL2

MMU Enabled, Translation Table @ 8000c000 Granularity 4KB, bits 40

Kernel entry accessibility W: 0 R: 0

Level 0, @8000c000: TTD 000000008000d003 Page! Next Level:

Level 1, @8000d000: TTD 000000008000e003 Page! Next Level:

Level 2, @8000e000: TTD 0000000000000611 Block Level 2, @8000e008: TTD 0000000000200611 Block

Level 2, @8000e010: TTD 0000000000400611 Block Level 2, @8000e018: TTD 0000000000600611 Block

Level 2, @8000e020: TTD 0000000000800611 Block Level 2, @8000e028: TTD 0000000000a00611 Block

Level 2, @8000e030: TTD 0000000000c00611 Block Level 2, @8000e038: TTD 0000000000e00611 Block

Level 2, @8000e040: TTD 0000000001000611 Block Level 2, @8000e048: TTD 0000000001200611 Block

[...]

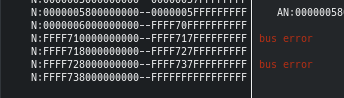

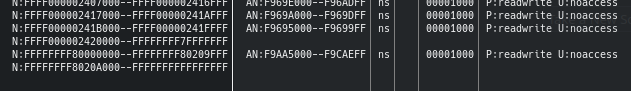

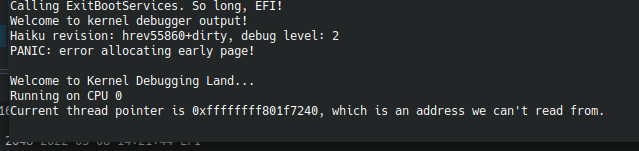

Additionally from the memory maps being dumped before, there is some useful information: addreses, exepcion level & MMU translation regime. At last, there is some code developed to handle the table descriptors, useful enough to able to perform a complete tablewalk and dump the whole translation table levels.

Some code base & information dumping, but no actual functional steps forward. Despite that… how about a PR to be in synch?